플랫폼

-

기술명

첨단 패키징 소재 - 웨이퍼 박형화 보호(TBDB, Temporary Bonding De-Bonding)소재

-

개요

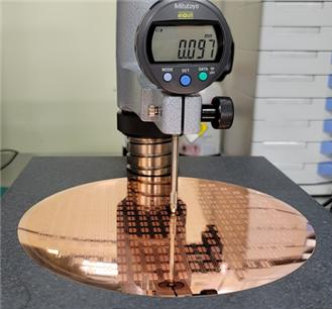

본 개발 소재는 액상출발 형태의 웨이퍼 백그라인딩 소재와 공정 소재로서, 물질간 계면에너지 및 탄성계수 조절 기술을 부여하여, 웨이퍼 백그라인딩 공정을 수행하기 전 웨이퍼 전면의 구조물을 액상 형태의 소재로 완전히 감싼 후 응고하여 구조물과 보호소재 사이의 빈공간을 없애고 후속 백그라인딩 시 힘의 편중을 최소화하여 웨이퍼의 파단을 방지하고, 두께 120 마이크로미터 이하급 고효율 웨이퍼 백그라인딩 공정을 위한 웨이퍼 전면 패시베이션(보호) 소재기술과 공정기술을 적용하여 두께 균일도를 확보함으로서 백그라인딩 수율 및 효율을 증가시킬 수 있음.

-

기술적 특징

기존의 수입의존 전면 보호 케리어 필름을 이용한 웨이퍼 백그라인딩 공정프로토콜에서의 기본 단위공정인 케리어 필름 본딩, 캐리어 웨이퍼 본딩, 백그라인딩, 디라미네이션, 클리닝, 다이싱테입 본딩, 다이싱, UV노출, 다이싱테입 디본딩의 9단계 공정을 1단계 예비연구에서 Bare 웨이퍼 대상 박형화(thinning)를 위한 액상출발 백그라인딩 코팅 소재 및 공정 호환성 확보된 사항을 바탕으로 레진 코팅, 캐리어 필름 라미네이션, UV노광, 백그라인딩, 다이싱, 필름 디라미네이션의 6단계 공정으로 단순화하여 사업화 진행함.

-

기술적 장점

본 개발 소재는 웨이퍼 백그라인딩 수행 전 전면 보호용 액상출발 소재로서, 응고된 후 웨이퍼의 백그라인딩 시 전단응력에는 강한 저항력을 보이며, 백그라인딩 수행 후 웨이퍼와의 수직분리 시에는 수월한 이형력을 보일 수 있는 계면에너지와 탄성계수를 조성해 주어, 웨이퍼 백그라인딩 공정의 안정성과 효율 및 수율을 높이는 동시에, 공정 간소화를 통한 비용 및 시간의 절감을 유도할 수 있음.

- 강한 백그라인딩 전단응력 저항성 및 수월한 박리성 확보를 통한 웨이퍼 백그라인딩 안정성과 수율향상 기대됨.

- 접착잔유물 제거 공정 생략을 통한 비용적, 시간적 경쟁력 확보 기대됨.

- UV경화형 웨이퍼 백 그라인딩 보호 소재는 웨이퍼 thinning 공정의 간소화와 안정화 및 생산성 및 수율 향상을 유도할 수 있음.

- 가격 경쟁적 측면에서 기존 제품 대비 획기적 우위의 경쟁력을 갖춤.

- 반도체 후 공정업체들의 문제점들을 보완하기 위한 R&D용역 서비스를 창출할 수 있음.

-

기술의 적용분야

제품화 적용

- 2.5D/3D IC 반도체 웨이퍼 백 그라인딩용 다목적 캐리어 필름 및 웨이퍼 백 그라인딩 전후공정설계는 반도체 후 공정에서 필수화 되어가는 소자 웨이퍼 thnining의 수요를 충족하는데 필수적으로 활용될 수 있음.

- 궁극적인 목표는 기존에 사용되던 장치 요소에서 발생했던 낮은 수율 및 균일도를 당사의 새로운 재료와 공정을 통해 향상시킴으로서 백 그라인딩 테이프, 라미네이팅 테이프, 다이싱 테이프 등으로 소모되었던 비용을 감소시키고 공정상의 안정성을 극대화시킴으로서 다방면으로의 제품 및 응용 가능성을 제시할 수 있음

- 위에서 언급했듯이 본 기술 개발의 성과로서 열안정성, 화학 안정성, 점착성 및 이형성이 우수한 코팅소재의 확보와 두께와 균일도 측면에서 우수한 코팅소재의 확보는 반도체 양산시스템에서 활용성이 매우 높은 다목적 캐리어 필름으로서 폭넓게 사용될 수 있음

- 반도체 패키지(Die Level Assy, TSV, Flip chip CSP, High Density & Fine pitch FC, Thin substrate CSP assembly chip, Lead Frame land grid array chip등)에 적용됨으로서, 보다 세밀하고 정교한 반도체 제품 생산에 기여할 수 있음.

- Tape Laminating과 wafer backgrinding 일괄 공정프로토콜(NNFC) 공정 호환 가능함.

- 3D IC, D PKG (TSV, WLP) 센서 등 In-line 구현으로 연계하여 고부가가치 반도체 기술 개발에 기여할 수 있음.

-

서비스 가능 범위 및

기술수준모바일 및 소형가전에서 요구되는 박형화를 위해 반도체 후공정으로서 소자웨이퍼의 백그라인딩이 필수적으로 요구되고 있으며, 본 과제를 통해 국산화 차세대 기술을 확보할 수 있음.

-

담당자 연락처

담당자 박재홍연락처 042-366-1731이메일 jhpark@nnfc.re.kr -

관련 이미지

- 소자웨이퍼

- Resin Coating

- Resin 개발 및 최적화

- Resin coating 및 demolding 공정 최적화 및 기구 개발

- 새로운 프로토콜상에서의 공정안전성 확보 및 균일도 호가보 레시피 개발

- Carrier wafer 또는 Tape Lamination & Curing

- Back grinding (water thinning)

- Wafer dicing

- Debonding